资料下载

超低功耗的27×1 PRBS发生器的设计资料及如何降低PRBS发电机的功耗

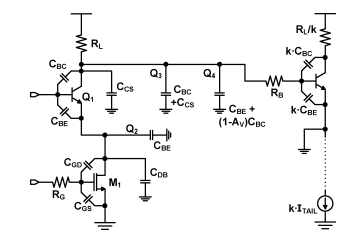

设计了一种超低功耗的27×1 PRBS发生器,具有四个适当延迟的并行输出流。它采用150GHz SiGe BiCMOS工艺制作,测量工作功率可达23Gb/s,四通道PRBS发生器从2.5V消耗235mW,每输出通道仅消耗60mW。该电路基于2.5mW BiCMOS CML锁存器拓扑,据我们所知,该拓扑表示锁存器工作在10Gb/s以上的最低功率。使用OCTC方法分析了低功耗BiCMOS CML锁存器拓扑结构。

索引条款电流模式逻辑,OCTC,伪随机位序列生成器,SiGe BiCMOS,技术缩放。

伪随机位序列(PRBS)发生器和校验器广泛用于测试宽带集成电路的正确功能,如重定时器、SERDES块和收发器。最先进的电路通常优于商业上可用的测试设备。为了避免这种测试问题,PRBS发生器可以集成在与被测器件相同的芯片上,用于内置自测试(BIST)目的。对于这些应用,重要的是,发电机能够产生尽可能长的序列,同时消耗低功率。早期高速PRBS发生器采用III-V HBT技术_1_1_1、2、硅双极_365331;65339;65339;5_以及最近SiGe双极_665331;65339;65339;665339;865339;8_8、SiGe双极65339;865技术。本课题组最近报道了一台具有21个序列长度_13、14_的80Gb/s PRBS发生器,但由于序列长度较长,其体积过大,功耗低,不能作为片上自测试模块。本文的工作是努力降低PRBS发电机的功耗,同时保持速度的一部分。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章