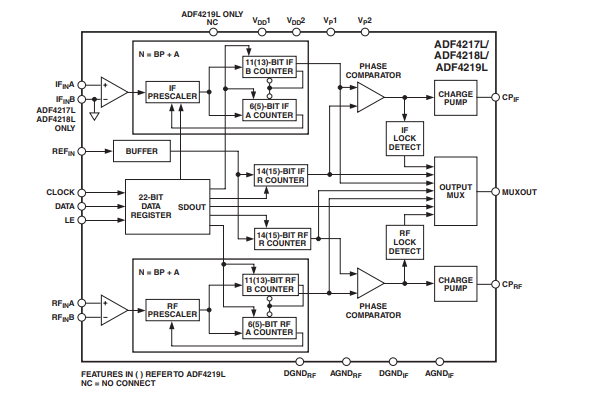

ADF4217L/ADF4218L/ADF4219L低功耗、双通道RF/IF整数N分频PLL技术手册

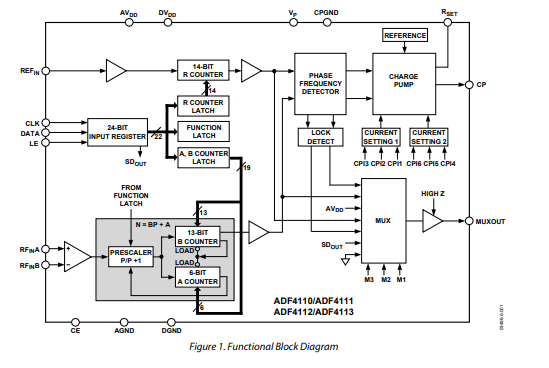

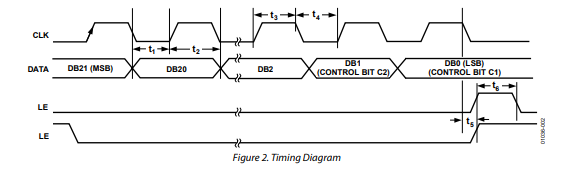

ADF4110/ADF4111/ADF4112/ADF4113单通道、整数N分频、550 MHz PLL,内置可编程预分频器和电荷泵技术手册

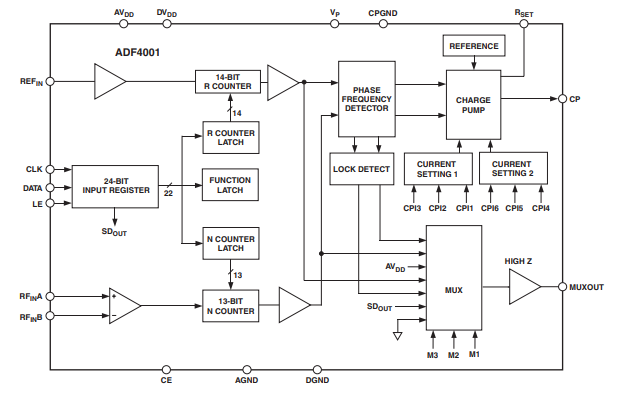

ADF4001 200MHz时钟发生器PLL技术手册

ADF4206/ADF4208双通道、整数N分频1.1GHz/2.0 GHz PLL技术手册

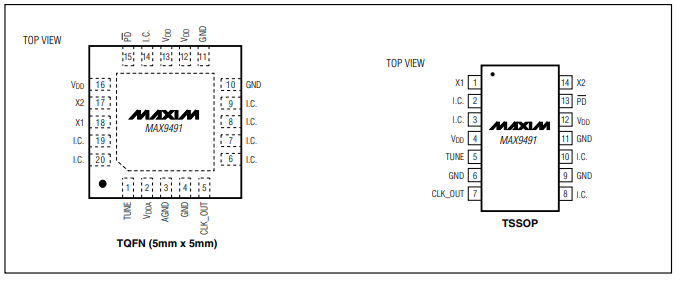

MAX9491工厂可编程、单PLL时钟发生器技术手册

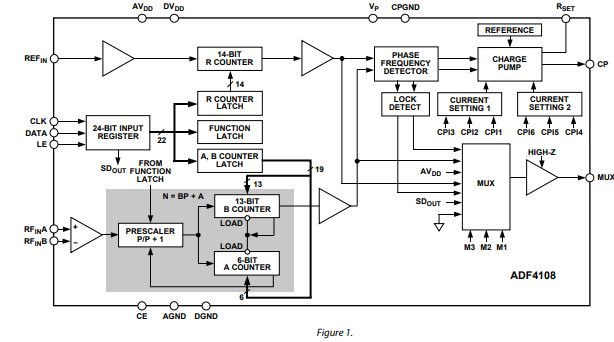

ADF4108 8GHz整数N分频PLL技术手册

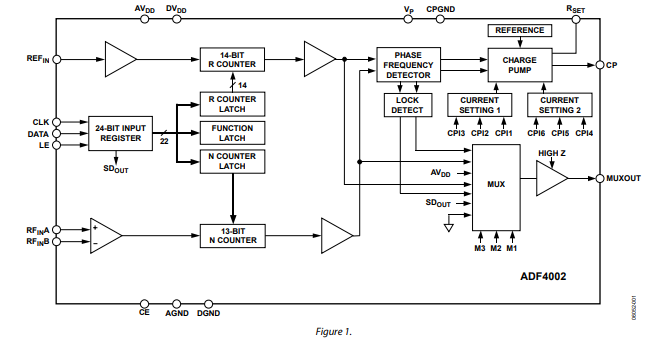

ADF4002鉴相器/PLL频率合成器技术手册

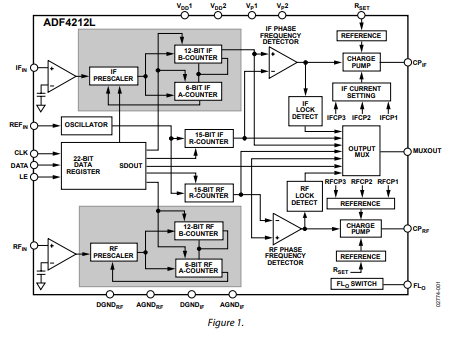

ADF4212L双通道、低功耗PLL频率合成器技术手册

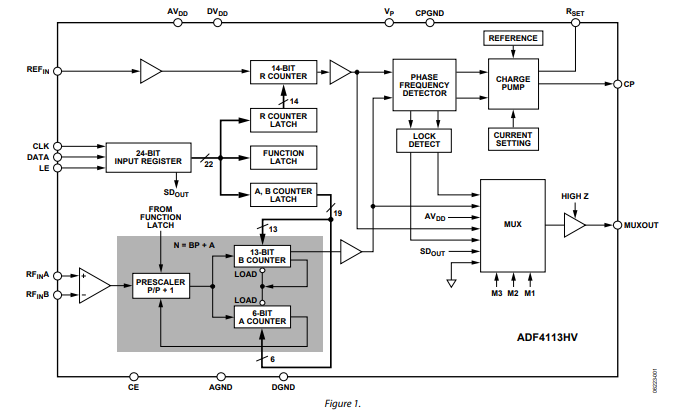

ADF4113HV高压电荷泵、PLL频率合成器技术手册

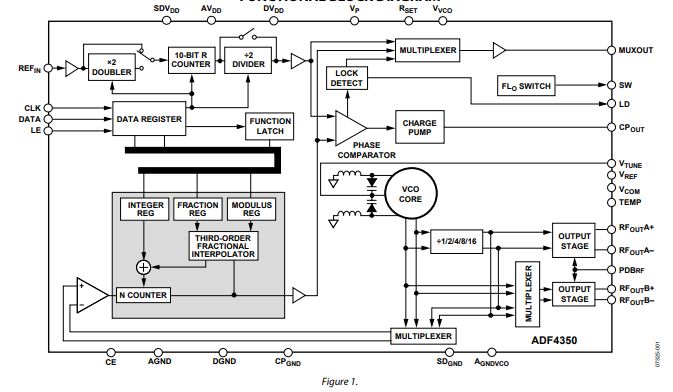

ADF4350集成VCO的宽带频率合成器技术手册

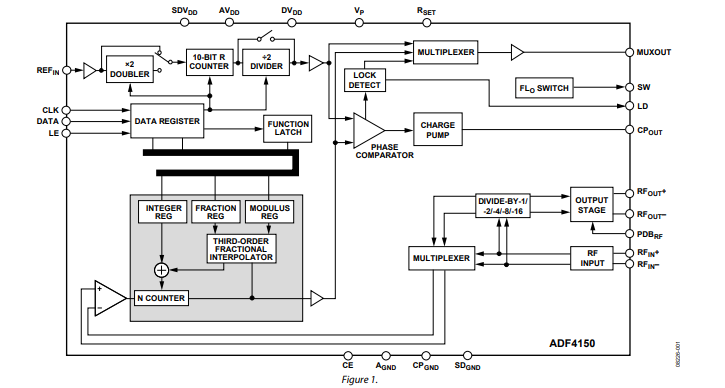

ADF4150小数N/整数N分频PLL频率合成器技术手册

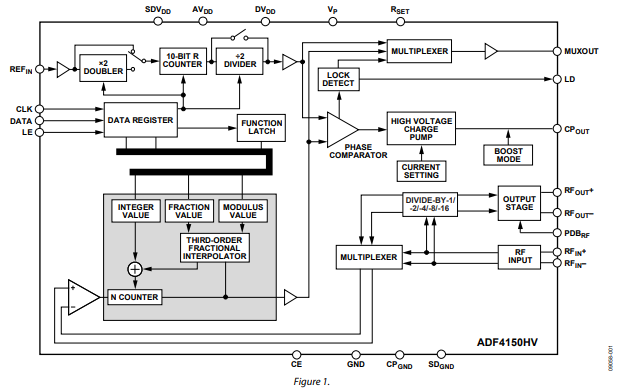

ADF4150HV高压小数N/整数N分频PLL频率合成器技术手册

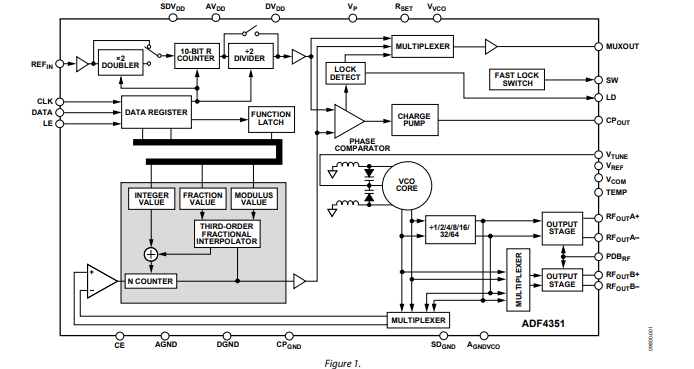

ADF4351集成VCO的宽带频率合成器技术手册

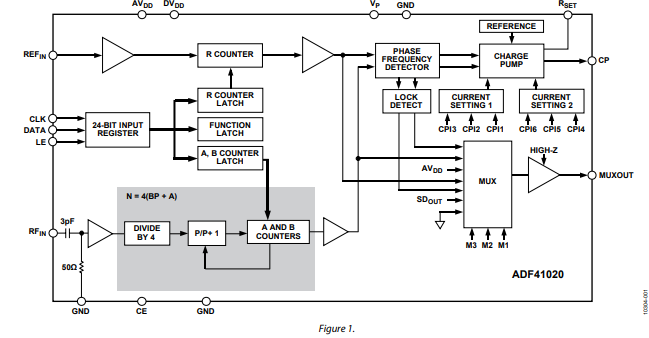

ADF41020 18GHz微波PLL频率合成器技术手册

ADF4151小数N/整数N分频PLL频率合成器技术手册

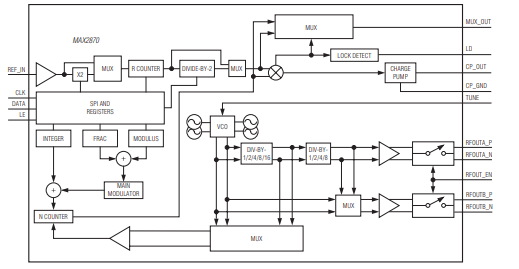

MAX2870 23.5MHz至6000MHz分数/整数N分频合成器/VCO技术手册

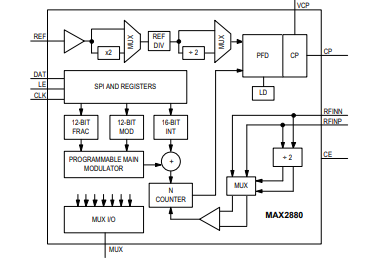

MAX2880 250MHz-12.4GHz、高性能、分数/整数型N分频PLL技术手册

ADF4155整数N/小数N分频PLL频率合成器技术手册

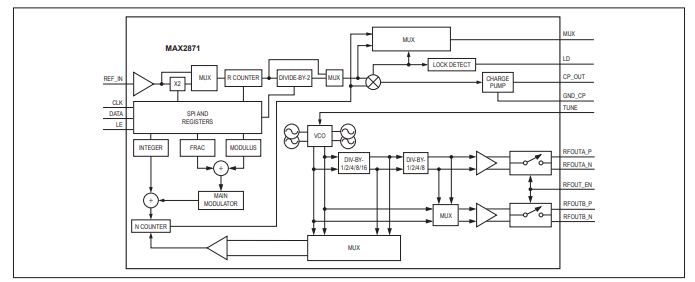

MAX2871 23.5MHz至6000MHz小数/整数N分频频率合成器/VCO技术手册

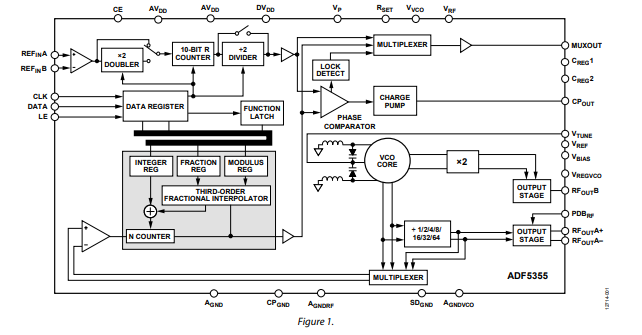

ADF5355集成VCO的微波宽带频率合成器技术手册