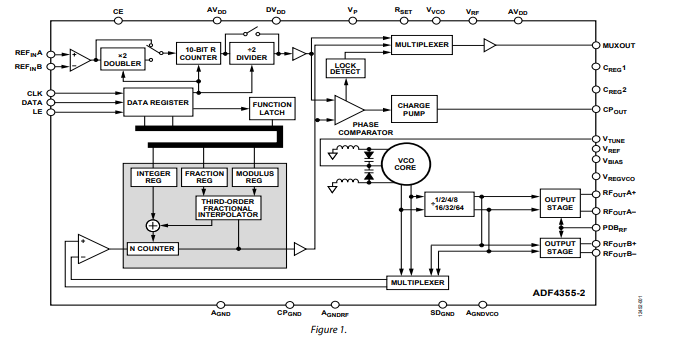

ADF4355-2集成VCO的宽带频率合成器技术手册

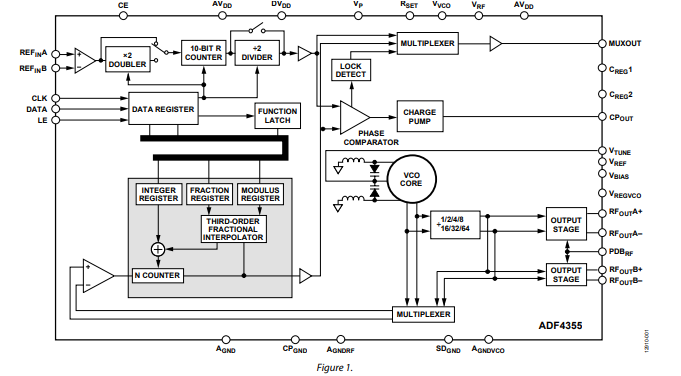

ADF4355集成VCO的微波宽带频率合成器技术手册

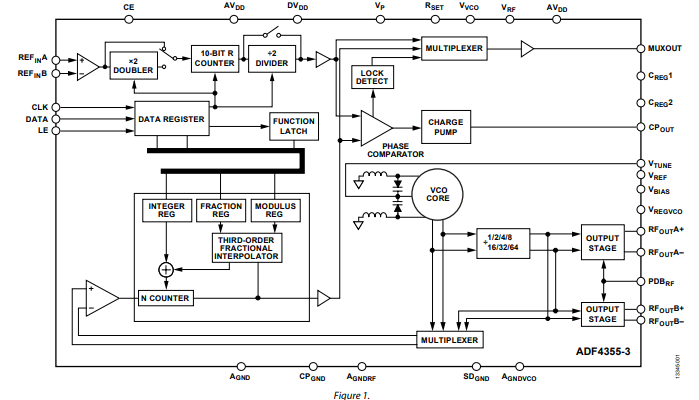

ADF4355-3集成VCO的微波宽带频率合成器技术手册

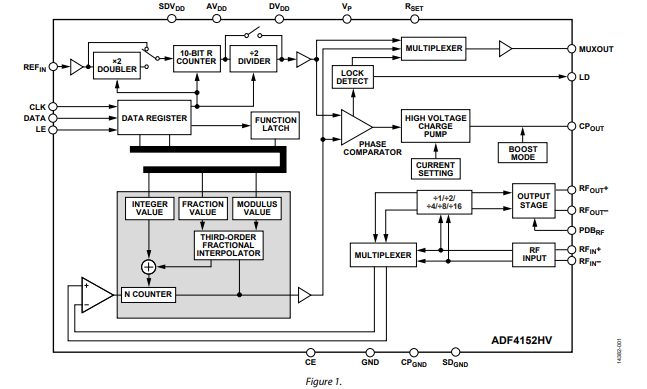

ADF4152HV 高压、小数N/整数N分频PLL频率合成器技术手册

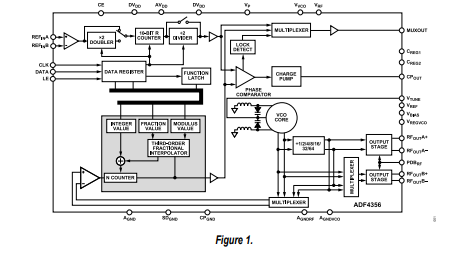

ADF4356集成VCO的6.8 GHz宽带频率合成器技术手册

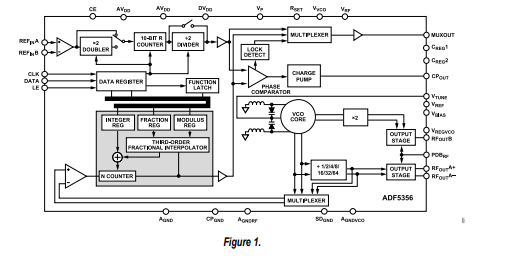

ADF5356集成VCO的微波宽带合成器技术手册

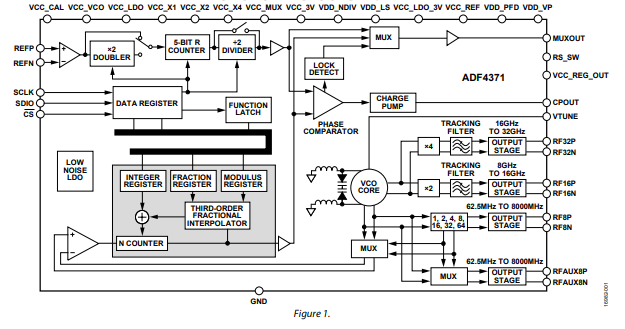

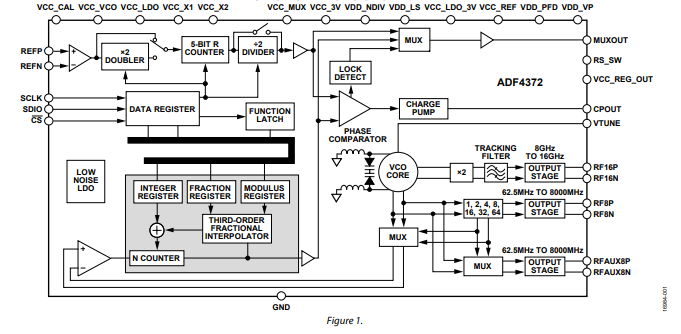

ADF4371带集成VCO的微波宽带合成器技术手册

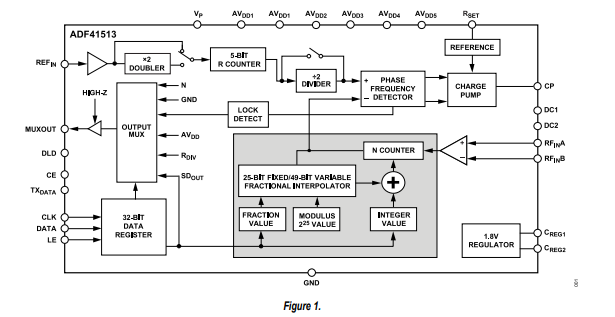

ADF41513 26.5GHz整数N/小数N PLL频率合成器技术手册

ADF4372带集成VCO的微波宽带频率合成器技术手册

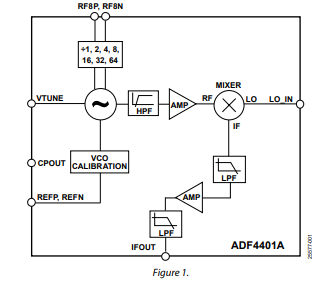

ADF4401A转换环路、PLL、VCO模块技术手册

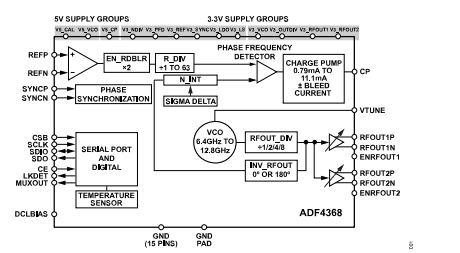

ADF4368集成VCO的微波宽带技术手册

ADF41510 10GHz、整数N/小数N分频PLL频率合成器技术手册

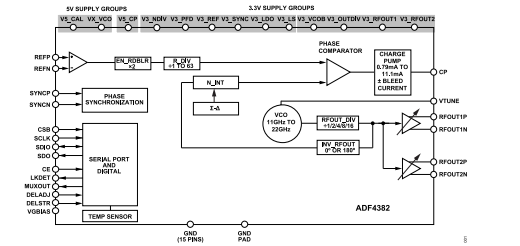

ADF4382集成VCO的微波宽带频率合成器技术手册

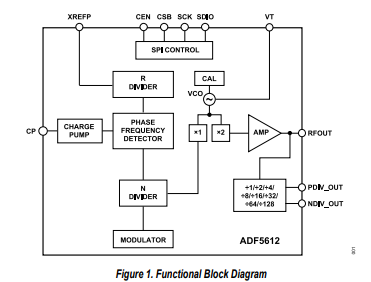

ADF5612集成VCO的微波宽带频率合成器技术手册

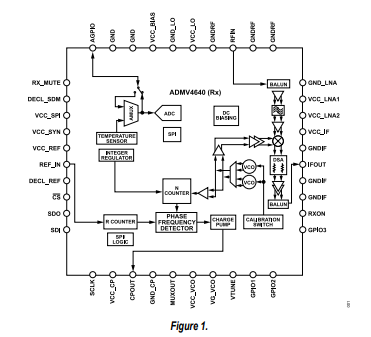

ADMV4640集成小数N分频PLL和VCO的Ku频段下变频器技术手册

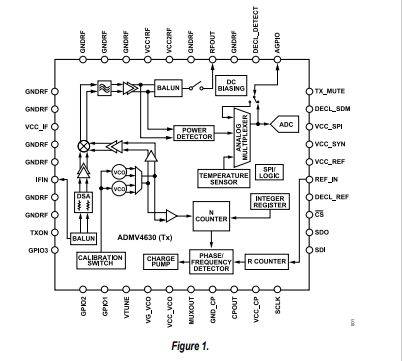

ADMV4630集成小数N分频PLL和VCO的Ku频段上变频器技术手册

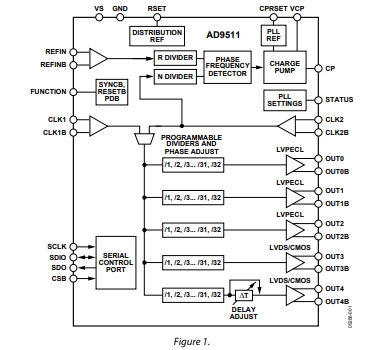

AD9511 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,5路输出技术手册

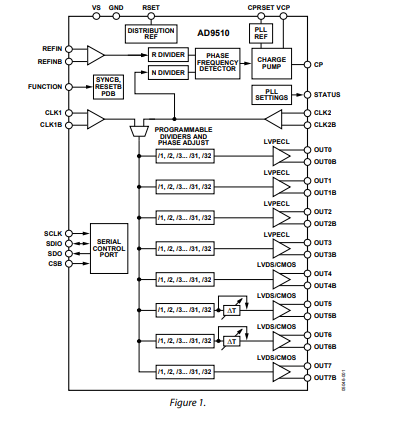

AD9510 1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出技术手册

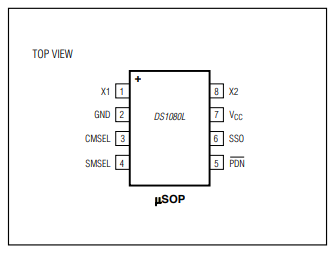

DS1080L扩频晶振倍频器技术手册

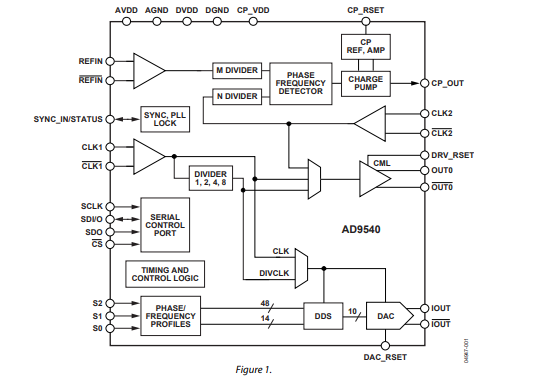

AD9540低抖动、基于DDS的时钟发生器和频率合成器技术手册