资料下载

×

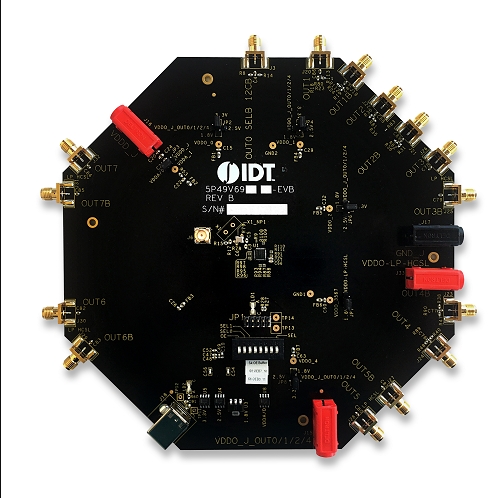

5P49V6967 VersaClock® 6E评估板数据手册

消耗积分:0 |

格式:rar |

大小:1.77 MB |

2024-05-09

这是IDT 5P49V6967 VersaClock 6E可编程时钟发生器的评估板。在整个 12kHz 至 20MHz 集成范围内,该器件的 RMS 相位抖动小于 0.5ps,可满足 PCI Express® Gen 1/2/3、USB 3.0 和 1G/10G 以太网的严格抖动要求。

特征:

3 个差分输出,能够使用 IDT Timing Commander™ 软件生成任何输出频率

4 个额外的 LP-HCSL 输出副本

用于输出的 SMA 连接器

当该板通过 USB 连接到运行 IDT Timing Commander 软件的 PC 时,可以对设备进行配置和编程,以生成具有一流性能的频率

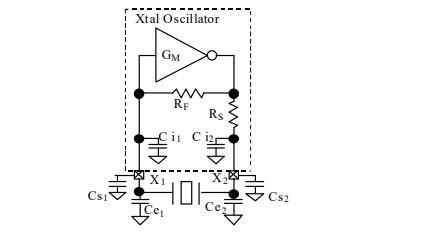

当不使用CLKIN/CLKINB时,安装在电路板上的25MHz晶振可以为器件提供参考频率

5P49V6967 VersaClock® 6E评估板:

以下是5P49V6967 VersaClock® 6E评估板数据手册技术文档简介图:

以下是5P49V6967 VersaClock® 6E评估板原理简介图:

下面是本文的下载链接,如有需要,大家可以下载哦:https://file1.elecfans.com/web2/M00/E3/6F/wKgZomY8lhOAX6e5ABxEfjM8GS8167.rar

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章