资料下载

×

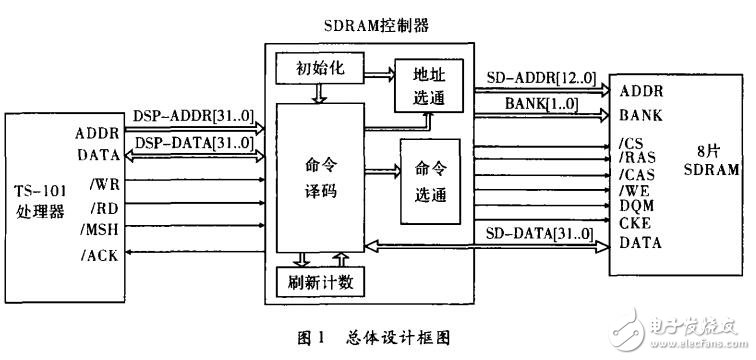

SDRAM控制器的设计

消耗积分:0 |

格式:rar |

大小:0.70 MB |

2017-11-28

在很多通信芯片及系统的开发中,常常需要用到存储容量大、读写速度快的存储器。在各种随机存储器件中,SDRAM的价格低、体积小、速度快、容量大,是比较理想的器件。但是,与SRAM相比较,SDRAM的控制逻辑复杂,接口方式与普通的存储器差异很大。为了解决这个矛盾,需要设计专用的SDRAM控制器,使用户像使用SRAM -样方便的使用SDRAM。考虑到控制器的通用性,本文中提出了一种通用的SDRAM控制器的FPGA设计,FPGA内部采用状态机的方式。该设计采用了AD公司的DSP处理芯片TS - 101作为主控系统。TS - 101虽然能直接访问SDRAM,但容量有限。这里将其外部SDRAM存储容量扩展到512Mbyte,使用的是TS - 101的主机(/MSH)空间,这是一个SRAM型的接口空间。在此设计系统中TS-IOI的系统时钟以及FPGA和SDRAM的时钟均为50MHz。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章