资料下载

×

CDCS503-Q1带有可选展频时钟(SSC) 的时钟缓冲器倍乘器的数据手册

消耗积分:0 |

格式:rar |

大小:0.48 MB |

2018-11-20

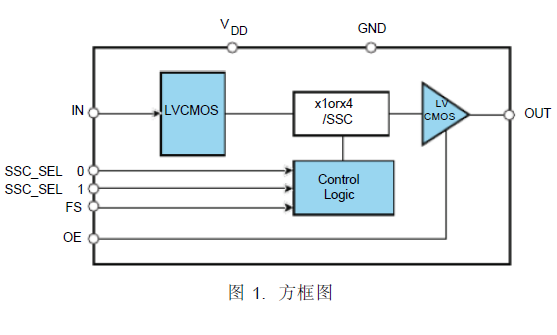

CDCS503-Q1 是一款带有可选频率倍乘的可展频、LVCMOS 输入时钟缓冲器。

它与CDCS502 共用主要的功能性,但是它使用一个LVCMOS 输入级而不是CDCS502 所使用的晶振输入级,并且CDCS503-Q1 有一个输出使能引脚。

此器件在输入上接受一个3.3V LVCMOS 信号。

这个输入信号由一个锁相环路(PLL) 处理,此环路的输出频率或者与输入频率相等或者被乘以因子4。

PLL 还可通过三角调制将时钟信号以输出时钟频率为中心扩展±0%, ±0.5%,±1%或者±2%。这样,此器件可生成介于8MHz 和108MHz 之间带有或者不带有SSC 的输出频率。

一个独立的控制引脚可被用于启用或者禁用输出。CDCS503-Q1 运行在一个3.3V 环境中。器件额定运行温度介于-40°C至105°C之间,并采用8 引脚TSSOP 封装。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章