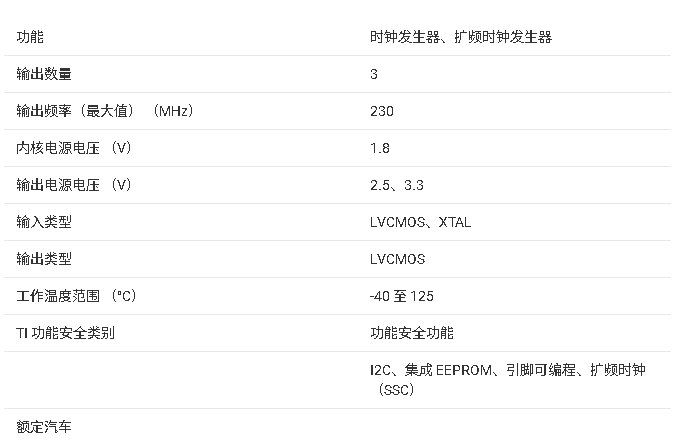

CDCE913-Q1和CDCEL913-Q1可编程时钟合成器技术文档总结

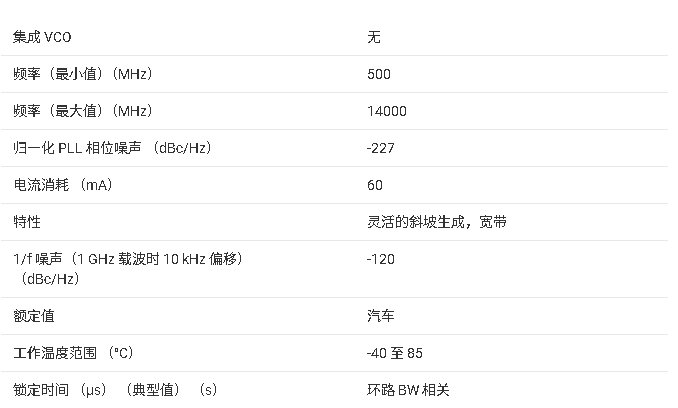

LMX2492/LMX2492-Q1 14 GHz低噪声分数N锁相环(PLL)芯片技术文档总结

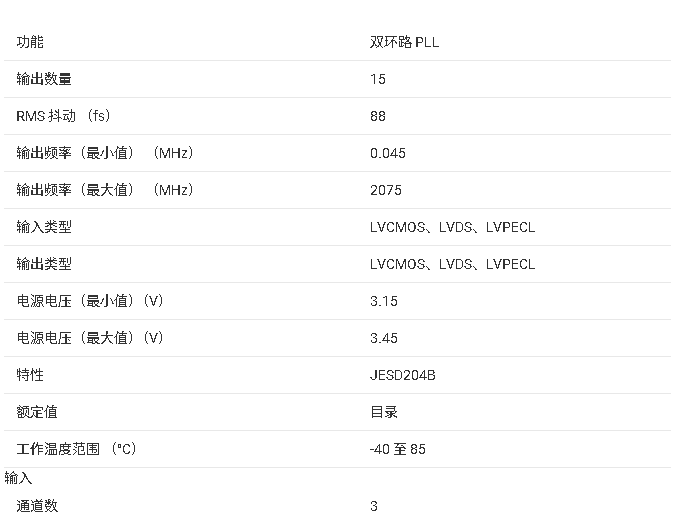

LMK04821 超低抖动合成器和抖动清除器技术手册

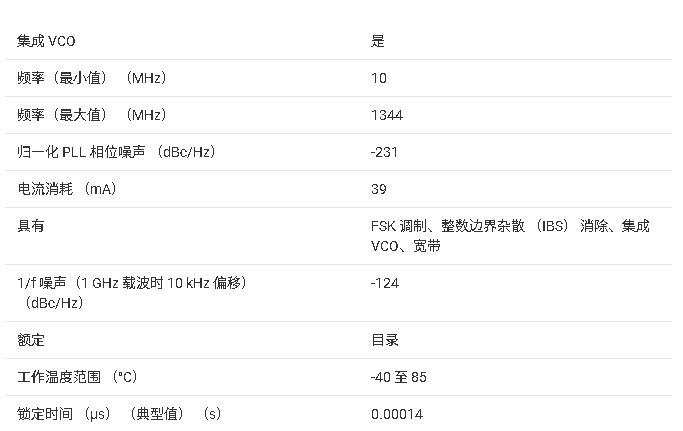

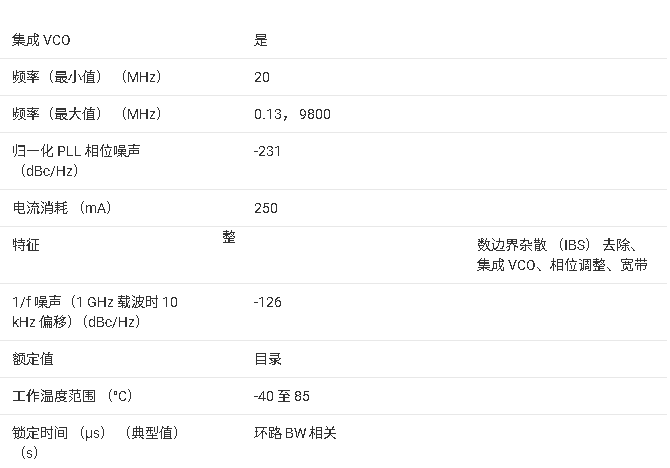

LMX2571 低功耗高性能射频合成器技术文档总结

CDCEL824 可编程双PLL时钟合成器技术文档总结

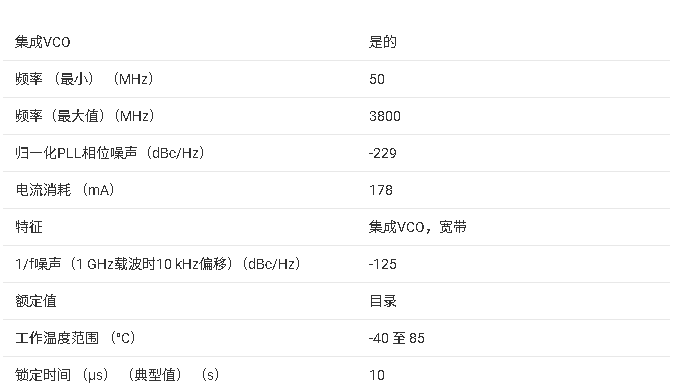

LMX2581E宽频带频率合成器技术文档总结

LMX2592 高性能宽带射频合成器技术文档总结

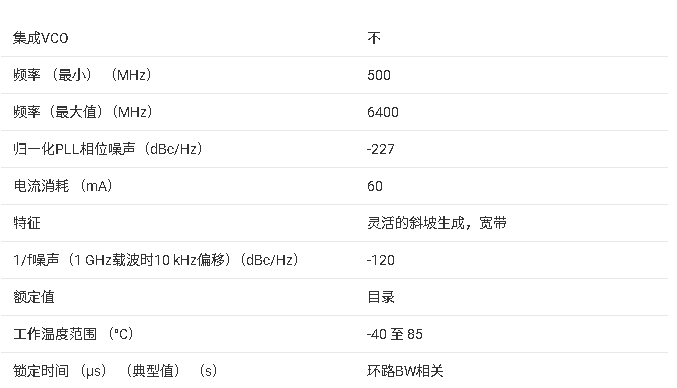

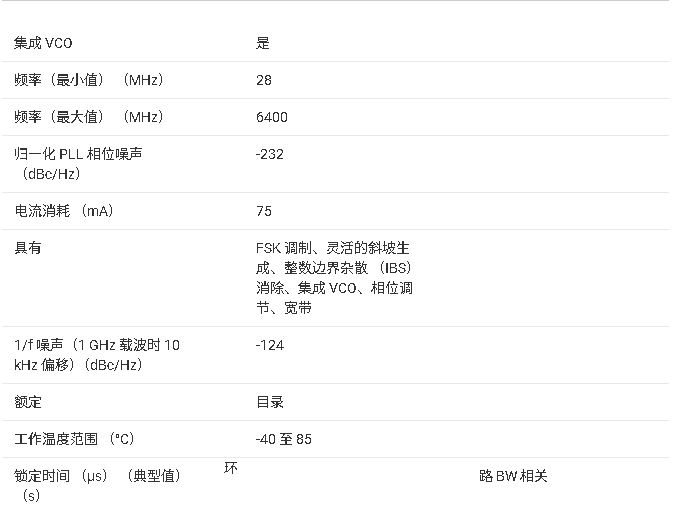

LMX2491 6.4-GHz低噪声RF PLL芯片技术文档总结

CDCE813-Q1 可编程时钟合成器与抖动清除器技术文档总结

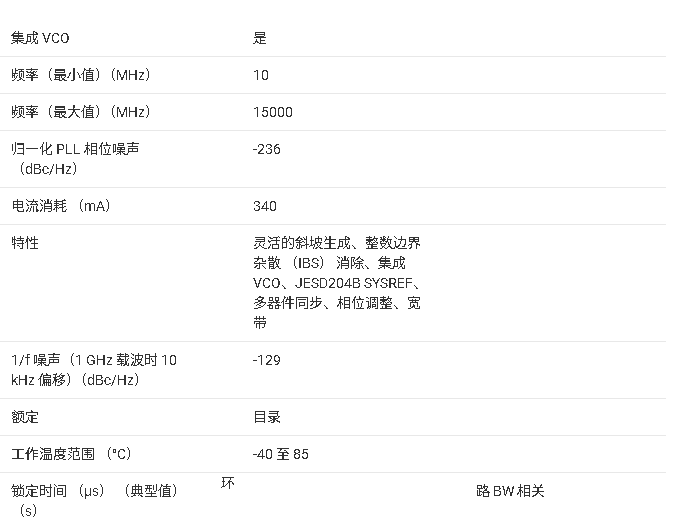

LMX2594 15-GHz宽带PLLATINUM™射频合成器技术文档总结

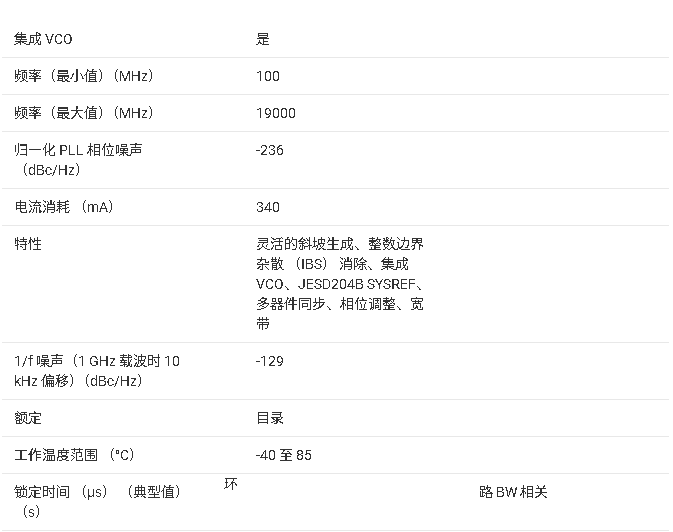

LMX2595 20-GHz宽带PLLATINUM™射频合成器技术文档总结

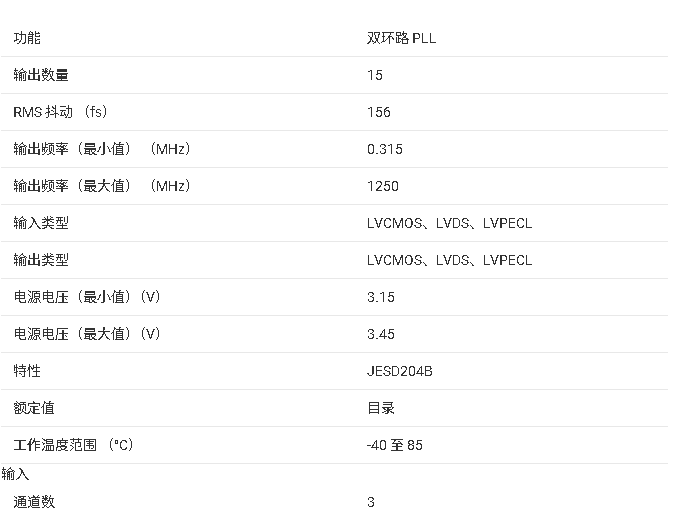

LMK04228 超低噪声双环PLL时钟抖动清除器技术文档总结

LMX2572 6.4GHz低功耗宽带射频合成器技术文档总结

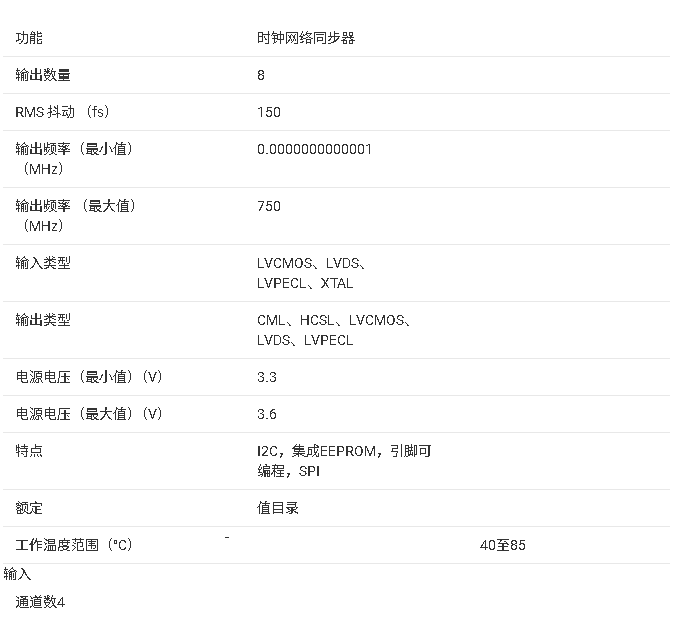

LMK05028 低抖动双通道网络同步器时钟芯片总结

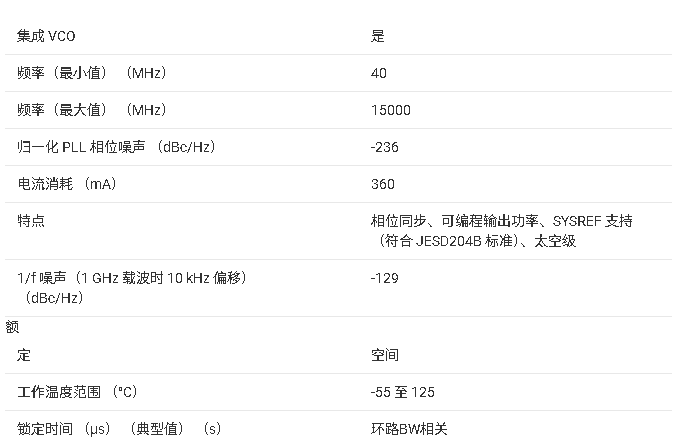

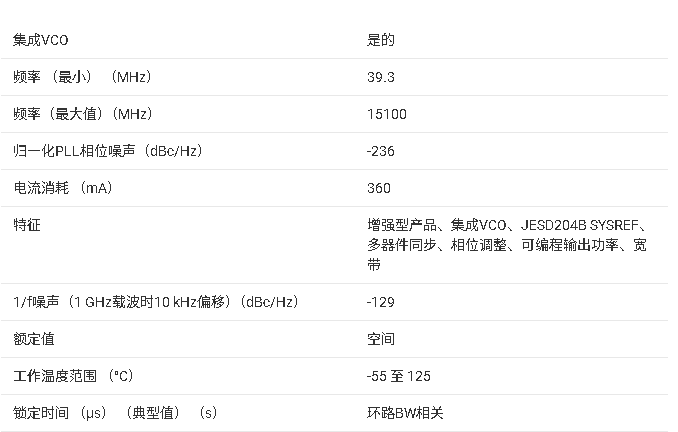

LMX2615-SP 空间级宽带合成器技术文档总结

LMX2694-EP 15-GHz宽频带PLLatinum™射频合成器总结

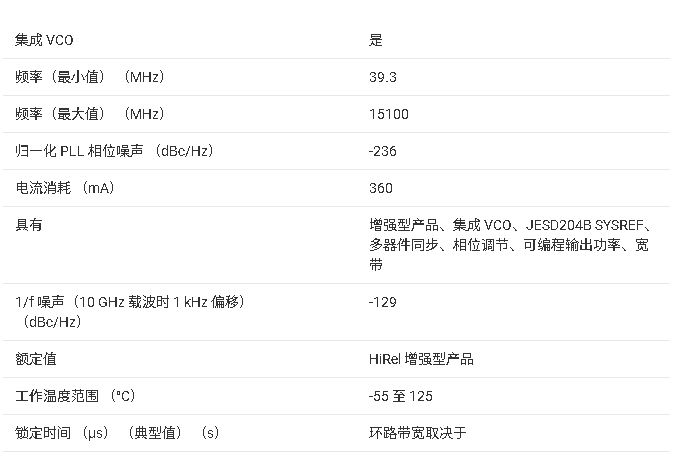

LMX2694-SEP 文档总结

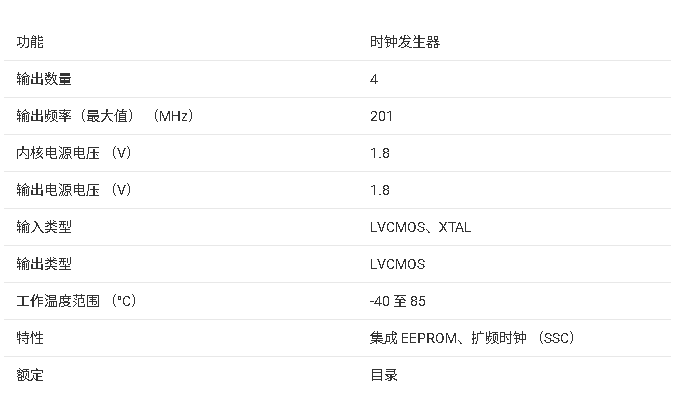

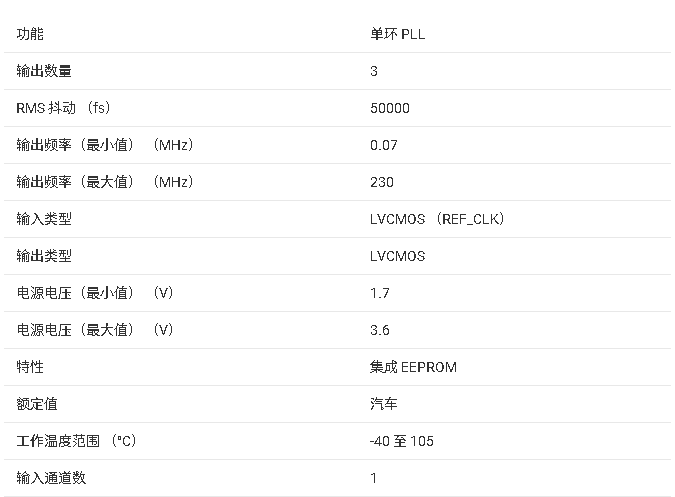

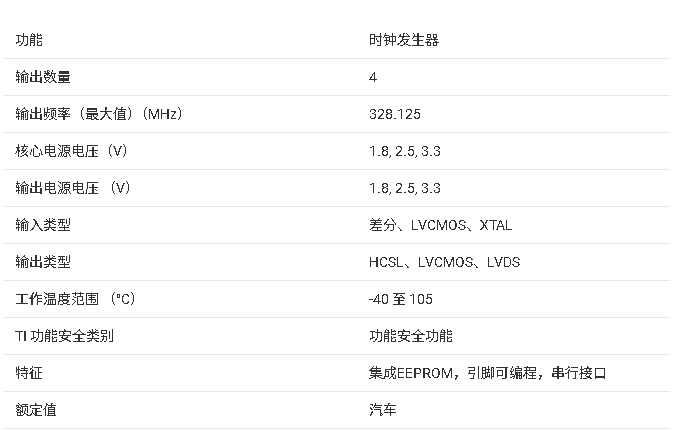

CDCE6214-Q1 超低功耗时钟发生器技术文档总结

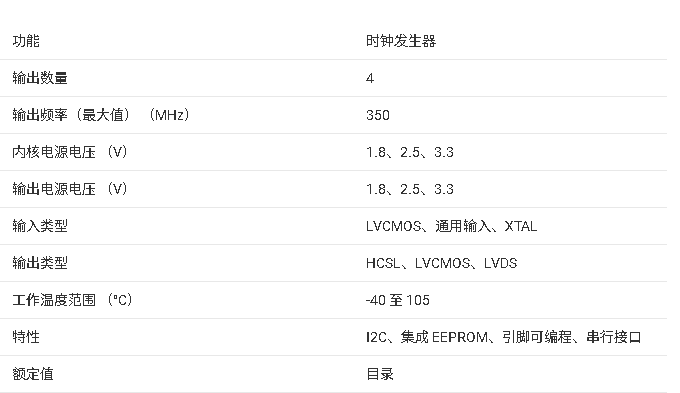

CDCE6214 超低功耗时钟发生器技术文档总结

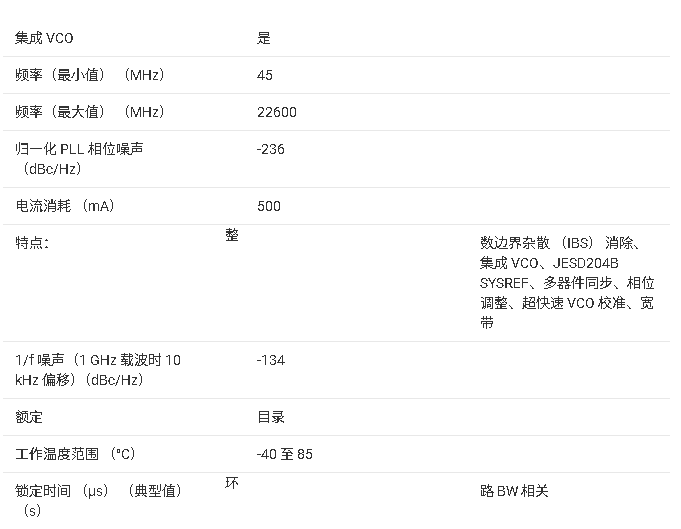

LMX2820 22.6 GHz宽带PLLatinum™射频合成器技术文档总结